http://www.angelfire.com/80s/sixmhz/tvscope.html

now I need a suitable TV to mess with

I guess its enough of offtopic for now

Moderators: BigEvilCorporation, Mask of Destiny

HardWareMan wrote: Second, we can made some big counter wich will count M68K clocks and will reset with M68K. Outputs of this counter can be passed thru 74x245 bus former to data line at some address. So, software always can get number of ticks goes from start of program (reset). I think it is more easy. And I can make this, if you can't.

I think, we must have some reserve of counter capacity, say 1 second will be enough. So, if CPU CLK=7,6MHz our counter must be 24 bit to fit that number. Or, you can use divider to divide VCLK by some constant.Jorge Nuno wrote:How many bits? 12 (CMOS 4040) ?

You can use sequence of move.w opcodes. For example:Jorge Nuno wrote:It shall be a wire mess, and yet, there is no guarantee that the HVcounter starts at the same time as this one, and you can't just read HVcouter and this counter simultaneously.

Code: Select all

move.w Counter,d0

move.w HVCounter,d1

move.w Counter,d2Code: Select all

move.w Counter,d0

move.w Counter,d1

move.w Counter,d2

move.w Counter,d3

move.w HVCounter,d3

move.w Counter,d5

move.w Counter,d6

move.w Counter,d7My tests indicate that when the VDP powers on, it starts pretty much anywhere within the frame. It certainly doesn't begin from a fixed point, IE, the beginning of a new frame. I'm running on a base MD1 with no TMSS, and every time I ran my ROM to capture data (which starts capturing a handful of cycles in), the HV counter data began from a completely different point in the frame.maybe by reading Hcounter value as soon as the system is powered ONBah there is almost no way to make a relation between [VDPstatus/HVcounter <-> Output signals

and measuring VDP reset signal in relation with video signals (this would also gives us the effective line number where VDP starts)

most probably, Hcounter is *always* reseted with the same value when the VDP resets also, it appears to be reloaded with 0xe4 (0xe9) each time it reaches 0xb6 (0x93)

how is that possible ?It certainly doesn't begin from a fixed point, IE, the beginning of a new frame. I'm running on a base MD1 with no TMSS, and every time I ran my ROM to capture data (which starts capturing a handful of cycles in), the HV counter data began from a completely different point in the frame.

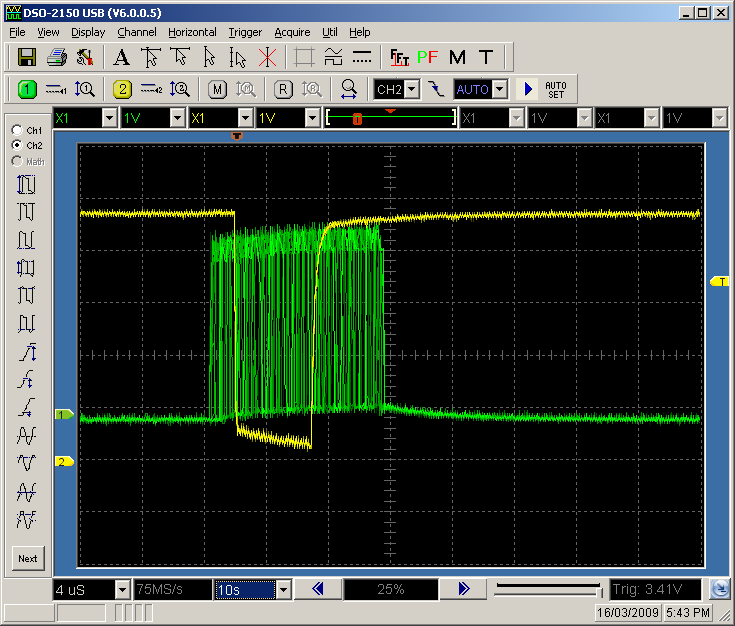

damn... this is smartI've constructed a test ROM which runs an active loop reading from the VDP status register, using machine code opcodes which leave various "target" bits of the 16-bit word region unset. This means those data lines are only asserted when transferring data from the VDP status register, so I can easily sample any of these lines with an oscilloscope, and know what I'm always looking at is the state of that bit in the status register of the VDP. Using this technique, it's possible to accurately match up readings from the status register to the various output signals from the VDP.

I had big expirience with build schemas that make raster TV signals. I can say that to implement additional reseting logic is not justified. Just make simple reset logic on needed condition. So, when you power up it, random state achieved. Then it will be count step by step at source clock and very soon all logic set to normal planned state. Usually it takes one-two frames to stabilize.Eke wrote:how is that possible ?

I mean, the VDP is logic hardware, and like any logic it *should* have a fixed reset state.. which includes internal counter registers as well

I don't see how possible it is to initialize registers with "random" values ? Maybe it's all matter of latency between the first read and the moment the VDP effectively started.

Also, the counters *have* to run at the same time the VDP generates the video signal so they should start running as soon as the /RESET line is disactivated.

What could be possibly done is to install a 3-position switch on this RESET line, first position connected to default (ie Master RESET line), others connected to ground/+5V (or whatever it is in a genny) ?

This way you could have code running and trigger some random VDP reset...