Page 2 of 2

Posted: Wed Feb 27, 2013 11:06 am

by r57shell

TmEE co.(TM) wrote:There is no FIFO on the DAC register

I know, but how you read sample from M68k memory?

Or your driver "lives" in M68k?

Read directly from M68k bank - not my way.

Because nothing aligned, and it will require many bank switching.

Posted: Wed Feb 27, 2013 11:46 am

by TmEE co.(TM)

I got a 256 byte buffer for mixing and playback

Posted: Wed Feb 27, 2013 1:00 pm

by Stef

You can here an example of a driver capable of 4 channels 8 bits PCM mixing with envelope support from SGDK:

http://code.google.com/p/sgdk/source/br ... 0_drv4.s80

Posted: Wed Feb 27, 2013 1:34 pm

by r57shell

PCM only driver - not cool.

Posted: Wed Feb 27, 2013 3:43 pm

by Stef

Indeed, but just to show the general idea of the algorithm used to deal with the bank switch. You can easily add and apply the same for FM/PSG stuff.

Posted: Wed Feb 27, 2013 5:45 pm

by GManiac

Really?

I see 24 there.

http://www.fileden.com/files/2009/4/23/ ... exing3.png

Guys, don't invent nonexistent things. 24 = 6 cycles * 4 operators and 23 is prime number

When I performed tests on hardware, I of course recorded the lowest YM frequency to look at sine template. I used 96 kHz sampling. Remember that real hardware frequency differs from ideal values like 53203424 blablabla Hz, and sound card is not ideal too. You get a deviation from ideal values, but this deviation is always constant for one console and one sound card. And it doesn't exceed 0.1%. Below the values for NTSC system are described.

My notes in Russian:

Считаем шаблон синуса по фазе:

Генерируем частоту Note=00001.

Расстояние между ступенькой вниз и вверх - 945004 семплов

Расстояние между ступенькой вверх и вниз - 945005 семплов

Было измерено на 5 периодах, т.е. погрешность очень низкая.

Т.е. частоту Ямахи можно считать равной 53260.75 с очень низкой погрешностью.

In English: I recorded Note = 1, Block = 1, Mult = 1. Expected frequency was near 0.05 Hz. One perriod took in average of 5 ones 945,004 + 945,005 = 1,890,009 samples in wave, it is 19,69 seconds. And real frequency is 0.0508 Hz. Channel frequency is 1048576 times more, so it is nearly equal to 53260.75 with high confidence.

Calculated ideal value is 53693175 / 7 / 24 / 6 = 53267 Hz.

It is VERY close to value above, deviation is 0.01%.

And yes...

r57shell wrote:I just tired in searching for precise info.

Common formula:

18 * (1024 - TIMER A) microseconds

Timer A - all 1's -> 18 µs = 0.018 ms

But, I think it is not precise. Where it goes from?

I suppose 18µ goes from 1s / 53267 Hz =

18,773349353258114780257945820114 µs

Notice that manual uses 8 Mhz Clock, so frequency will be 55,555.55 Hz and 1s / 55555 Hz = 18 µs exactly.

Posted: Wed Feb 27, 2013 6:15 pm

by TmEE co.(TM)

I was surprised when I looked at the tolerance factors of oscillators used in MDs. They are are +/-50ppm. I expected 100 or more.

Posted: Wed Feb 27, 2013 6:26 pm

by r57shell

GManiac wrote:Really?

I see 24 there.

http://i1.imageban.ru/out/2013/02/27/2e ... 0fad9f.png

GManiac wrote:

Guys, don't invent nonexistent things. 24 = 6 cycles * 4 operators and 23 is prime number

This is cycles

between channels. So prime is ok.

GManiac wrote:

Calculated ideal value is 53693175 / 7 / 24 / 6 = 53267 Hz.

It is VERY close to value above, deviation is 0.01%.

Intersting info.

I have done some profiling.

Testing game without Timer A check in emulator.

During sample playing, and when no sample played.

Measurement: DAC update calls in second.

Code: Select all

Game Not played Playing Used

Ultimate Mortal Kombat 3 (U) ~17278 ~7500 ~6944

Comix Zone (U) ~20250 ~11500 ~11111

Donald In Maui Mallard (E) ~24500 ~13500 ~11111

So, these games use the samples within its capabilities.

Posted: Wed Feb 27, 2013 7:01 pm

by GManiac

One more time

http://www.fileden.com/files/2009/4/23/ ... exing3.png

You don't see the picture to the left, so your 23 cycles are not confident.

r57shell wrote:GManiac wrote:Guys, don't invent nonexistent things. 24 = 6 cycles * 4 operators and 23 is prime number

This is cycles

between channels. So prime is ok.

So how do you think

operators are implemented? Do you think it's a solid process which longs 23 cycles for 4 operators? Prime is NOT ok here. Heh. Even if there is additional processing, old processors work only with even numbers of cycles. Z80 and 6502 have quant of 2 cycles, not 1. I think, YM2612 is not exception.

Anyhow, I've already proved that real frequency is 53260 Hz and there are 24 cycles per channel.

Posted: Wed Feb 27, 2013 7:19 pm

by r57shell

GManiac wrote:

You don't see the picture to the left, so your 23 cycles are not confident.

I see rising edge of green line on left border of image.

One more time:

http://savepic.ru/4139148.png

GManiac wrote:

So how do you think operators are implemented? Do you think it's a solid process which longs 23 cycles for 4 operators? Prime is NOT ok here. Heh.

Many options: 4*5+3, 1+4*5+2, 2+4*5+1, 4+4*4+3, even 4*1+19

How do you explain that pulse width differs? (time when green HIGH)

On left it's 5 cycles, on right it's 6 cycles. Same on

this picture.

Posted: Wed Feb 27, 2013 7:38 pm

by HardWareMan

I suggest to return to the

DIE shots and recover a circuit diagram of the crystal. The truth is out there. (c)

Posted: Wed Feb 27, 2013 8:12 pm

by r57shell

That's not for me

. Do it yourself.

Posted: Wed Feb 27, 2013 10:04 pm

by Eke

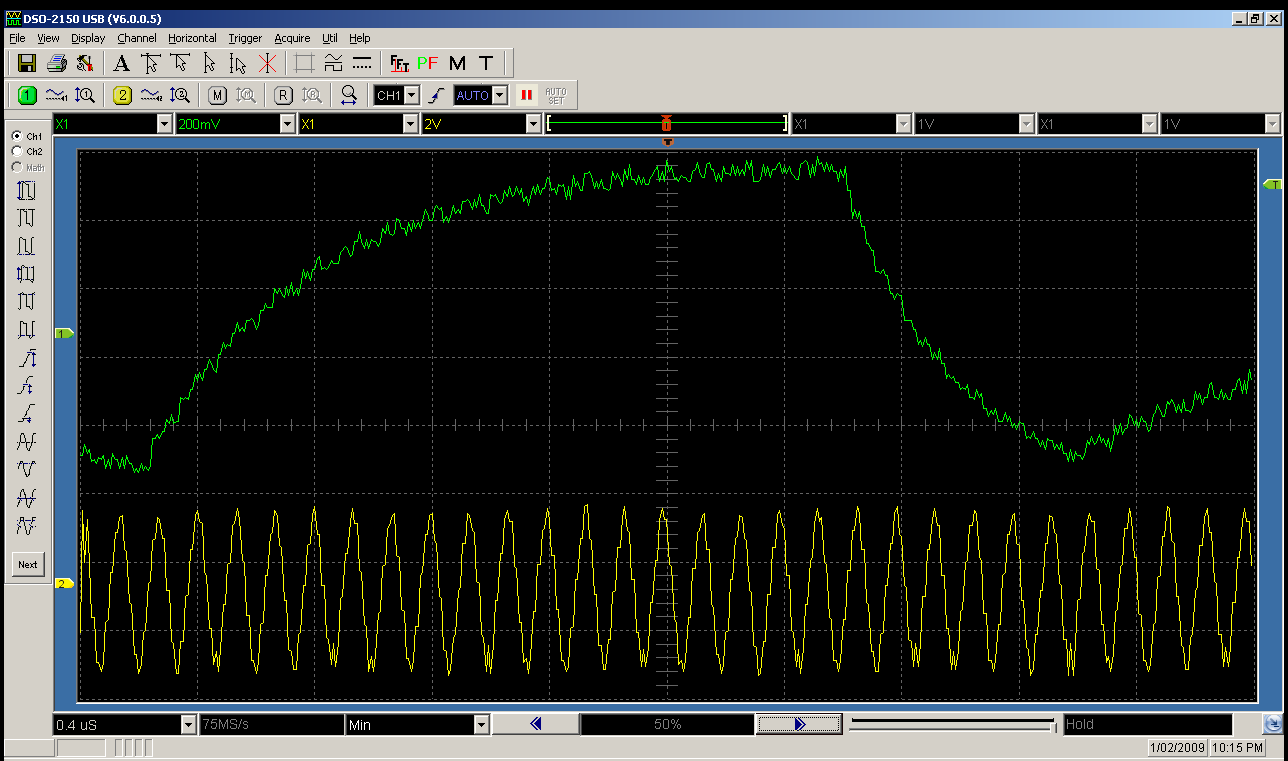

r57shell wrote:

How do you explain that pulse width differs? (time when green HIGH)

On left it's 5 cycles, on right it's 6 cycles. Same on

this picture.

i would say this is caused by the imprecision of the model 1 dac output

this also makes clocks couting quite unprecise: you can not be sure where the next channel output really starts since it depends on the output rising time

on the 2nd picture you posted, the output could actually start one clock earlier than where the trigger is set

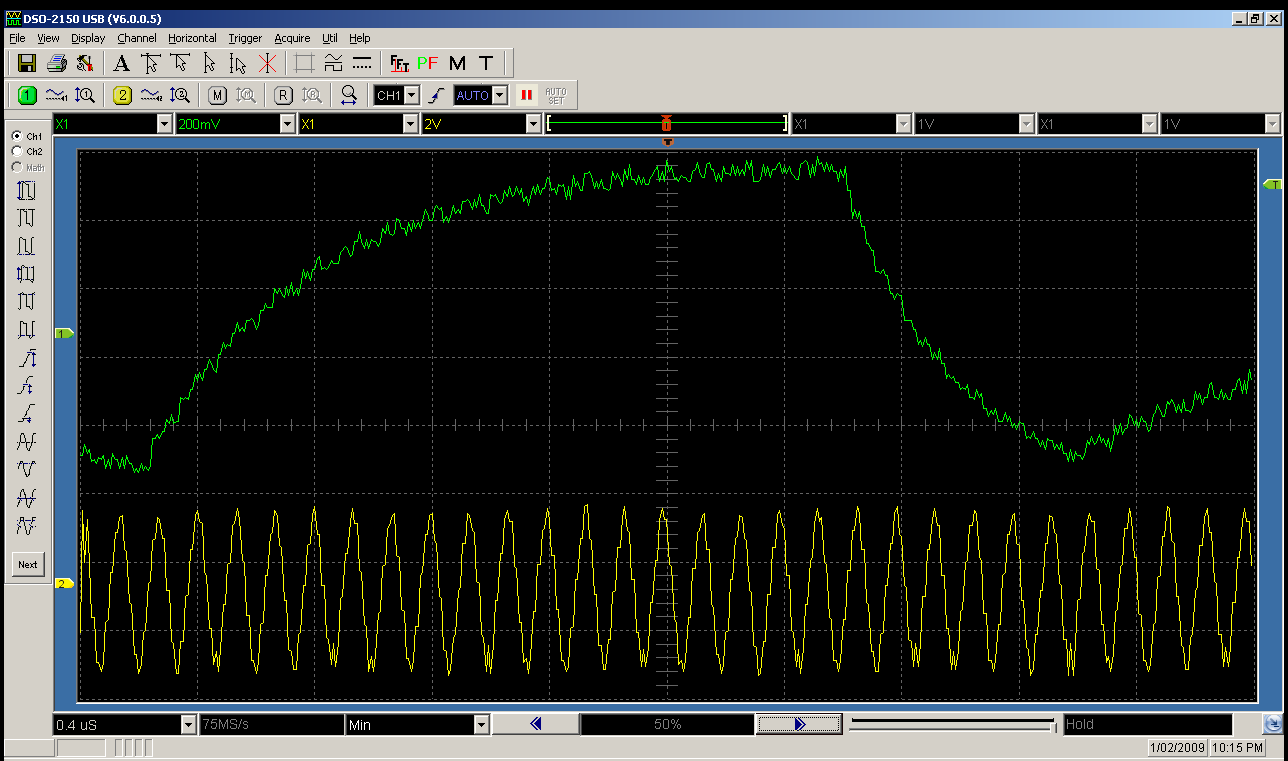

the model 2 dac is very different and somehow more precise, as seen in this pic

... as you can see, it's actually 24 clocks on this picture, so I think it's safe to assume it's the correct divider, especially when it has already been confirmed by several different people

Posted: Wed Feb 27, 2013 10:53 pm

by Chilly Willy

And this is why I use a 300 MHz OScope.