As previously stated in the FMDrive Vst thread, a simple way to implement the ladder effect is to add the clean output with the following...

(same behavior is observed on the hardware when you mute a channel, you still ear the distorted part at lower volume..)

This will produce an almost similar signal, spectrum and sound wise.

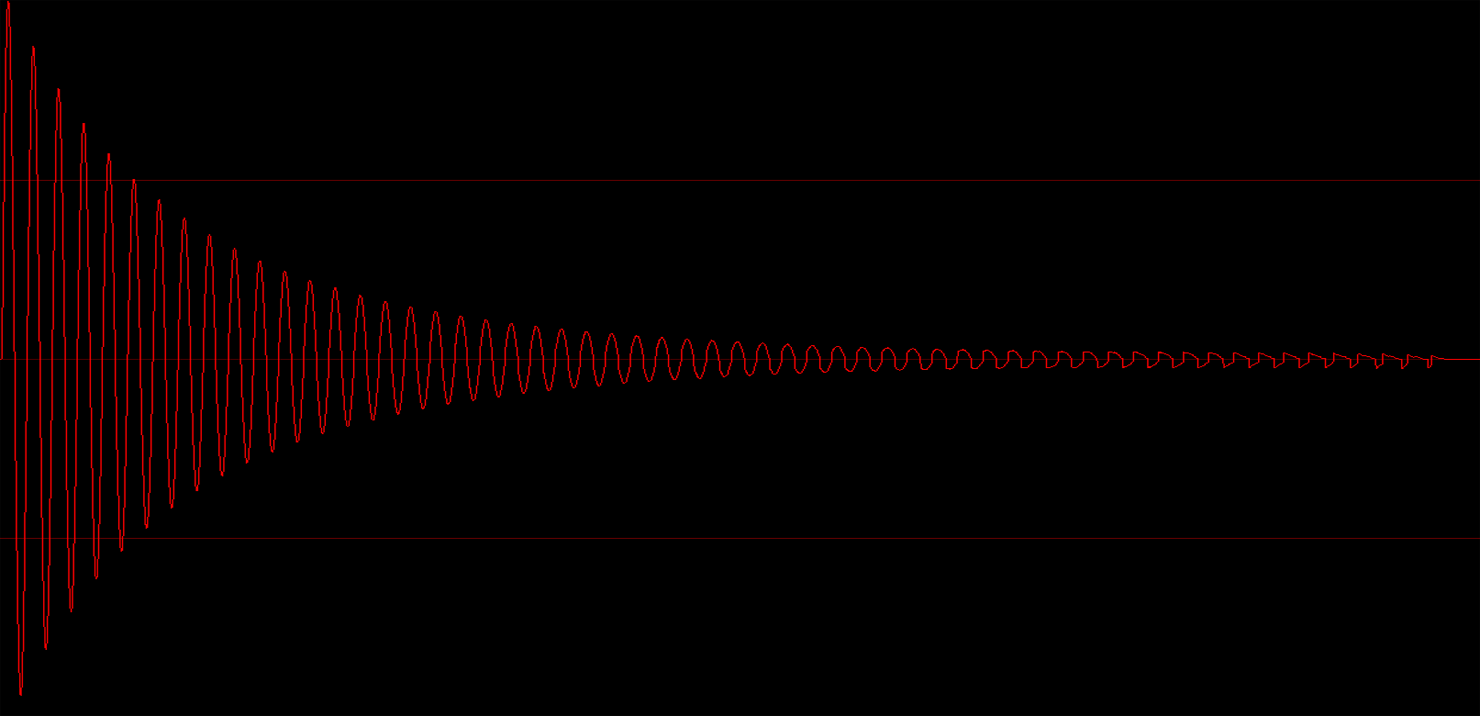

WAV recordings:

Megadrive PAL model 1 recording

FMDrive MD1 mode recording

and for the sake of comparison here is a clean signal from a YM2164 (from a FB01 unit)

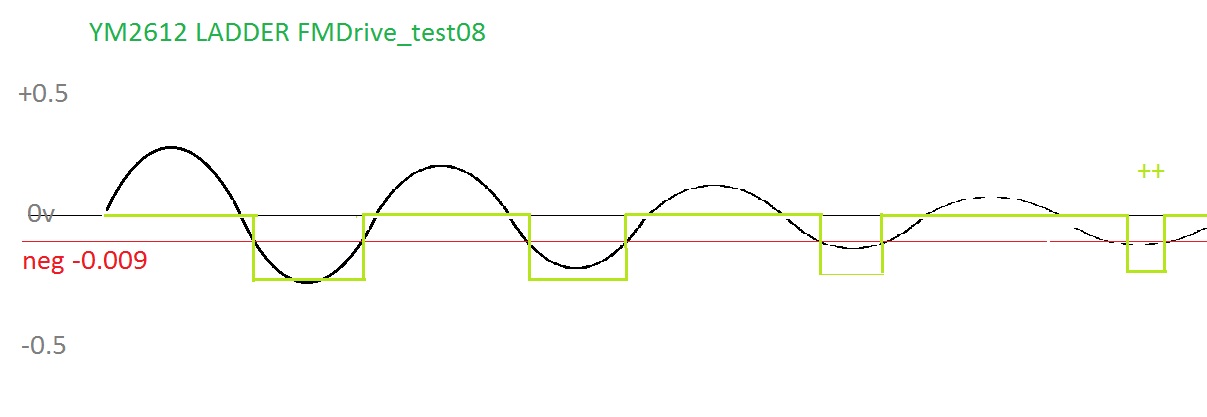

We will do something when the output is negative...

--------------------------------------------------------------------------------------

Ladder output:

-Let's consider the pure clean sine wave signal is going from max +1 to -1

as "sineout"

-Make a condition:

If sineout goes down past -0.009 then output a negative voltage almost 50 times lower then the clean maximum signal.

Else output 0.0 (and this will also prevent audio clicks)

Now let's see what happens to the "Ladder output"...

As you can see on the graphic, as the amplitude of the sine goes much lower, the period where the condition is true will also reduce..and this is what we clearly ear at the end.

green is our "Ladder output".

Note that you will also need to filter a bit (lp filter) the ladder output before adding to the clean signal.

Code snippet from FMDrive..

If you make any use of this, credit would be nice

Code: Select all

//Start of very fast ladder code

while( --sampleFrames >= 0 ) // sampleFrames = how many samples to process (may change). repeat (loop) that many times

{

sineout = *in; // max -1 +1

//ladder condition, VCC or GROUND

if (sineout<-0.009f)

{ladder=-0.02f; // output is almost 50 times lower than the clean signal, can be adjusted or optionally controlled..

}

else

ladder=0.0f; // grounded no signal

*ladder_out = ladder; //then filter this before adding to sineout

ladder_out++;

in++;

}