doragasu wrote:

as I wrote here[/url], I have observed (using a logic analyzer) just the opposite: #LDSW is lowered for even addresses, and #UDSW is lowered for odd addresses.

Seems like you are confused, from what you wrote in the post you linked, you actually observed the opposite i.e

UDSW being lowered for even addresses, which is indeed correct behavior

doragasu wrote:

I was wrongly assuming that when writing to even addresses, #LDSW was active, but it is #UDSW line the one that is lowered! I

Also note that when doing a word write, both signals are asserted, although technically the address is even (A0=0 internally).

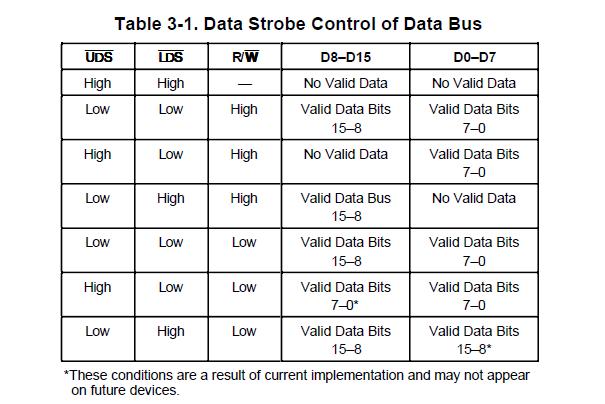

Actually, those signals are just strobes that indicate which part of the data bus (low or high) hold valid data, as documented below from the 68k User Manual.

- 68k_strobe.jpg (47.11 KiB) Viewed 50070 times

68k being a BIG Endian CPU, high byte (D8-D15) is stored at even address (ADDR) and low byte (D0-D7) is stored at odd address (ADDR + 1) where ADDR is address on external bus (VA1-VA23).

And to be nitpicking, there aren't any signals named #LDSW or #UDSW, there are #UDS, #LDS and #RW controlled by 68k CPU then #LWR and #UWR which are generated by VDP using 68k signals.