I wasn't planning on posting this until it was a lot more cleaned up, but I can see there's a lot of interest in this area right now, and I'm very short on time, so here you go:

http://nemesis.hacking-cult.org/MegaDri ... esting.zip

http://nemesis.hacking-cult.org/MegaDri ... esting.zip

Consider this an alpha version. This increasingly misnamed test ROM contains over 100 VDP test suites, each of them usually containing half a dozen or more tests, which verify many, many points of VDP behaviour surrounding port access. The goal is for it to test for every kind of behaviour which can be observed through VDP port access. This means it has no pure rendering tests, but it has many many other tests which involve how the VDP processes commands, and what information it returns, under all kinds of crazy corner cases.

I used this ROM as my primary code-based testing platform for VDP port access testing while developing my emulator Exodus, and I rely on it heavily as a regression tester for my emulator. There are still a bunch more tests I want to add to this ROM, in particular it needs some tests surrounding the HV counter, but it does a lot as it stands. There are a lot of completely undocumented things this test ROM demonstrates the behaviour of, including crazy things like port writes during DMA fill operations.

What I want from this ROM in the end is to have every test nicely documented, and all the expected results explained, so someone can go through the tests and understand how to design a VDP core so it can pass every test. That hasn't happened yet. Expect a lot of incorrect nonsense and guesswork written down inside the notes within each test. In fact, a lot of the tests will have incorrect information. Sometimes I designed a test to prove something worked a certain way, and ended up discovering that it didn't, so some comments may actually indicate the reverse of the true result. Unfortunately, the final correct comments usually only ended up as source comments within my VDP core, so until I manage to get Exodus ready for its source release, the documentation to describe why certain tests produce the results they do are somewhat lacking. The test results themselves however are valid, and they all pass on the hardware, with a few exceptions:

1. The Genesis 3 fails quite a few tests, as it actually has an 0x80 byte VSRAM, not a 0x50 byte VSRAM like earlier VDP models.

2. The three tests which perform data port writes during a DMA fill operation fail occasionally. I'm working on making these 100% stable.

3. The DMA Fill FIFO usage test gets the first write byte order reversed intermittently on the real hardware (and Exodus) due to timing sensitivity. This is an old test, I need to modify it to make it stable.

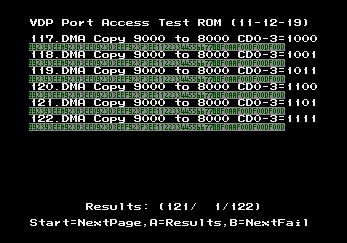

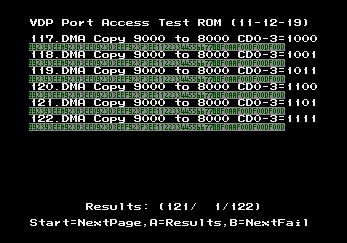

This test ROM was developed alongside my emulator, so it has a major home field advantage, but Exodus currently passes 121 of the 122 active test suites, the failing one of which is highly timing sensitive and I know is failing due to known timing errors in my M68000 core. For reference, Kega Fusion only passes 17, and other emulators like Gens and Regen are in a similar region. RetroCopy does pass the most of any other emulator out there, but it's still only somewhere in the 40's or 50's from memory. Note that there are a number of tests that cause current emulators to fail. Kega gets screen corruption partway through. Regen locks up on one test, and RetroCopy crashes on another. Look in the main source file for notes on which tests have issues. You can disable them if you want to do a build that'll work in those emulators.

Anyway, these tests should shed a lot of light on quite a few of the topics you're currently talking about. I'm happy to answer questions about any of these tests, or to describe the inner workings of specific parts of the VDP in greater detail, as much as I understand them at this point anyway.

Edit: The file I linked to was an old build that I remembered had a critical bug that prevented it working properly, so I've uploaded a new version with the error fixed. I've also added a screenshot and fact-checked the actual results from running this build.