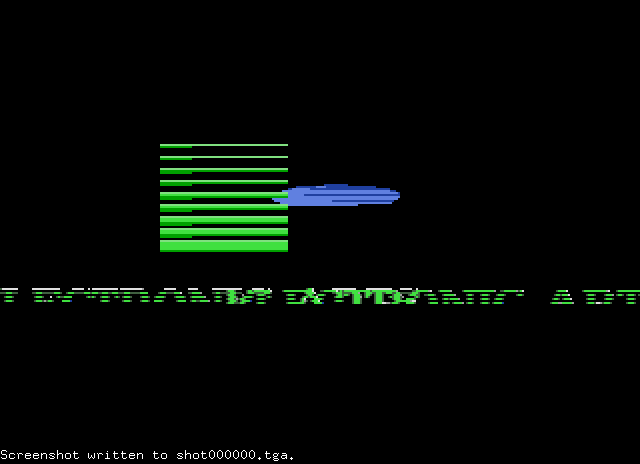

In my last post I mentioned that the flipping EA logo (at the start of many genesis games), is corrupted in dgen/sdl.

Stef said:

I have been reading Charles' VDP notes and found some reference to what Stef may be referring to:The EA logo is just a problem with write to VDP CTRL port. I don't remember the detail but i know this has something to do with VDP internal command state (first or second command word about to be written).

Looks like this is gnu syntax asm, that would be: mov #$91809280 -> $00C00004. So if you move a 32-bit data value into a memory address it writes twice. In the above case once at 00C00004 and again at 00C00006.Since the 68000 treats 32-bit memory access as two 16-bit operations,

you can program two registers at once:

; Set split point bits for both window registers

move.w #$91809280, $00C00004

I found the following code, which seems to tally up:

This seems correct. I have tried changing the order of the writes, with no joy.extern "C" void m68k_write_memory_32(unsigned int address, unsigned int value)

{

md::md_musa->misc_writeword(address, ((value >> 16) & 0xffff));

md::md_musa->misc_writeword((address + 2), (value & 0xffff));

}

So does anyone know anything about this EA logo bug?

Thanks